英特尔7nm等同于台积电的5nm?ASML揭晓答案

2021-04-10

ASML目前已然成了全球最大的光刻机设备供应商,半导体产业的源头支柱企业,不管是苹果的M1芯片,还是高通的骁龙888芯片,都是在ASML的光刻机下诞生的。光刻机市场上,ASML已经占据了全球62%的市场份额,更不用说EUV更是独此一家。

ASML的主要客户有台积电、三星、英特尔和中芯国际等企业,虽然光刻机的订单不成问题,但供货可不是一天两天的事。从订单到交货最长达两年,价值1.2亿美元的EUV更是包含10万多零部件,需要约摸40个集装箱运输。而且这其中大半零部件都来自于美国,这也会为何美国可以限制光刻机出口的原因。

ASML不仅生产光刻机,对半导体制造的研究也没有落后,那么在他们看来,这几家主要的半导体制造厂商的技术上有哪些异同呢?ASML技术开发中心负责人以及公司副总裁Anthony Yen在近期一次采访中说道,英特尔在5nm的工艺上已经落后于竞争对手,7nm也没有开始大规模量产,但由于他们更高的设计规则,英特尔的7nm是与台积电和三星的5nm相差无几的。

随着AMD在台积电的先进制程帮助下,移动与桌面端CPU都已经开始采用7nm工艺,而反观英特尔,移动端好不容易用上了10nm,而桌面端CPU仍在采用打磨已久的14nm工艺,比如即将于3月30日正式发布的Rocket Lake-S系列。虽然英特尔已经对14nm进行了多次迭代,但在用户眼中看来,这次“挤牙膏”未免太久了一点。

一只脚迈入全面10nm

英特尔虽然在7nm上坎坷不断,但好在也即将进入全面10nm的阶段了。近期外媒VideoCardz公布了或于今年第四季度发布的Alder Lake-S CPU的泄露信息。从公布的消息上来看,这款CPU采用的并非如今Tiger Lake移动处理器上的10nm SuperFin技术,而是10nm的SuperFin加强版。

从上图中可以看出,在新技术的加持下,英特尔再度将单线程性能提升了20%,多线程性能提升最高至两倍,而且支持最新的PCIe 5.0、Wi-Fi 6E、Thunderbolt 4和DDR5。而新CPU的接口也将换为LGA1700,供搭载英特尔600系列芯片组的主板使用。但从业内人士透露的消息来看,很可能只有高端Z690主板才会提供DDR5内存支持,而低成本的Z690主板仍可能仅支持DDR4内存。据了解,这是由于DDR5内存的量产不确定性所致,也给了英特尔和主板制造商更高的市场灵活度。

VideoCardZ同样爆料第十三代芯片Raptor Lake-S将在2022年正式发布,很有可能依旧采用10nm的SuperFin加强版,而7nm的SuperFin加强版可能得等到之后的Meteor Lake-S处理器才会面世。

密度不输人,命名吃了亏

那么制程落后的英特尔就一定比台积电和三星要差吗?也不尽然,说英特尔制程落后倒不如说是吃了命名的亏。从1960年代以来,半导体行业就一直在用物理参数作为制程技术的代名词,也就是晶体管栅极长度。这一代名词已经从80年代的微米级到了如今的纳米级,却也逐渐开始偏离原本的含义,更近似于一个商业用词。如今最先进的制程已经达到5nm,台积电等半导体制造商更是开始研究2nm和3nm,也给人以半导体技术即将到达界限的假象。

依照Anthony Yen的观点来看,ASML坚信摩尔定律至少可以再坚持10年,而且将与3D集成技术共同推进半导体产业的演进。与此同时,不少人也在呼吁用新的方式来衡量制程节点技术的发展,英特尔正是其中的主要号召者。

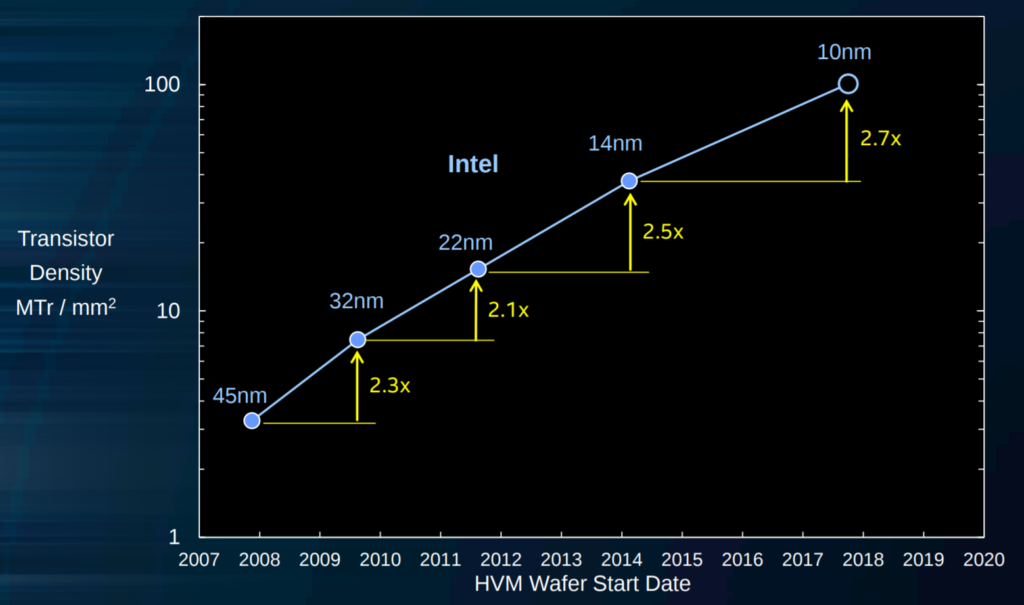

英特尔高级研究员和制程架构与集成主管Mark Bohr早在2017年就号召用标准化的密度指标来衡量制程与摩尔定律曲线的关系。制程已经换代,晶体管密度却没有变化的情况也不是没有。因此他主张利用MTr/mm2(每平方毫米内百万个晶体管)作为了逻辑晶体管密度的单位,除此之外再单独给出SRAM的密度数据。

英特尔制程晶体管密度曲线 / Intel

以这种单位来比较的话,英特尔在每个制程节点上的晶体管密度提升都是十分可观的,比如从14nm到10nm,晶体管密度就有了2.7倍的提升。英特尔一直在打磨的14nm晶体管密度为37.5MTr/mm2,而10nm下的晶体管密度已经达到100.8 MTr/mm2。

而台积电的第一代7nm制程N7FF仅有96.5 MTr/mm2的密度,之后引入EUV光刻机后的N7FF+(7nm+)才达到113.9 MTr/mm2的密度,这也是目前AMD主要采用的工艺。台积电的6nm过渡工艺的密度则在114.2 MTr/mm2左右,也是联发科天玑1100手机处理器所用的工艺。

台积电在2020年中宣布,其5nm制程的逻辑密度是7nm(N7)制程的1.8倍,因此初步估计晶体管密度在173 MTr/mm2左右。相较同样推出了5nm的三星,后者5LPE制程的晶体管密度只有126.53 MTr/mm2左右。不过此前三星也提到5LPE与7LPP相比,多数设计规则都是兼容的,意味着5LPE更像是一个全面引入EUV光刻机后的制程翻新而已。

曾任英特尔CEO的Brian Krzanich曾提到与10nm相比,英特尔的7nm将有2.4倍的密度提升。而上一任CEO Bob Swan则在19年末提到,英特尔不会在7nm上追求2.4倍或者2.7倍的提升,而是与5nm一样追求2倍的的提升。由此预估,英特尔7nm的晶体管密度大约在202到250 MTr/mm2左右。

这下可以看出英特尔在制程命名上的劣势有多大了,其他的半导体制造商在密度提升上并没有这么激进,可能在小幅提升后就换个了数字预示新的制程节点。而英特尔在制程命名换代上却追求的不是小提升,只能通过改善性能和功耗在已有制程上不断添上“+”号。以14+和14++为例,英特尔用了更大的栅极间距来换取高频性能的提升,以至于10nm刚推出时,甚至性能还比不上14nm++。

去年IEEE发布的一篇论文中也提到了密度指标的问题,这篇论文的作者之一也是台积电的研究人员。该文章主张从L(逻辑)、M(内存)和C(连接)的密度来衡量制程。L即逻辑晶体管的密度,这也类似于英特尔主推的密度指标,M即主存储器(也就是片外DRAM)的密度,C即逻辑单元与主存储之间的连接密度,这样当下的一些制造技术可以用[38M,383M,12K]这样的方式来表述,也可以让人看出3D集成技术对密度的影响。如此一来这些半导体公司依然可以用他们喜欢的命名来推销技术,但这一密度指标也可以作为客户和用户提供更清晰的比对。

小结

尽管英特尔的7nm得到了ASML的肯定,但半导体是一个瞬息万变的市场,推迟了制程进度的也不是台积电。要知道在目前的路线图下,英特尔的7nm制程从预计从2022年才开始加速量产,2023年才进入全面量产,而到了2023年,台积电早已实现3nm制程的全面量产,哪怕只有1.5倍的密度提升也足以超过英特尔。

好在现在英特尔哪怕制程落后,也不用太过担心竞争力落差。3月24日,英特尔新任CEO Pat Gelsinger已经宣布将与台积电展开合作,负责代工2023年的客户与数据中心CPU。如此一来,在2023年英特尔既能全面用上自家的7nm制程保证利润率,又可以借助台积电彼时5nm之后的先进制程来保证竞争力。就拿AMD来说,Zen 2系列CPU的CCD由台积电的7nm制造,但I/O却是基于GlobalFoundries的12nm/14nm工艺,这种做法对于Chiplet的小芯片设计来说也将愈发常见。

对于过去设计与制造僵化的英特尔,如今的英特尔不仅开放自己的代工业务,更是毫不避讳地将自己的产品交由第三方代工,未来的英特尔摆脱“牙膏厂”名号的希望正在不断放大。